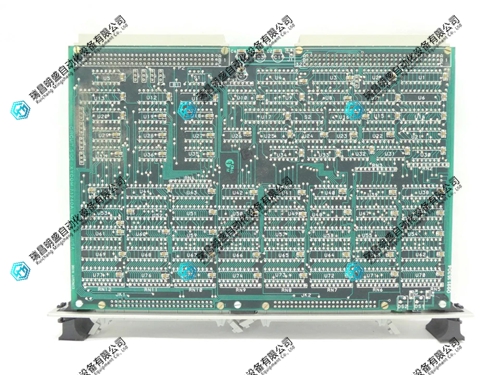

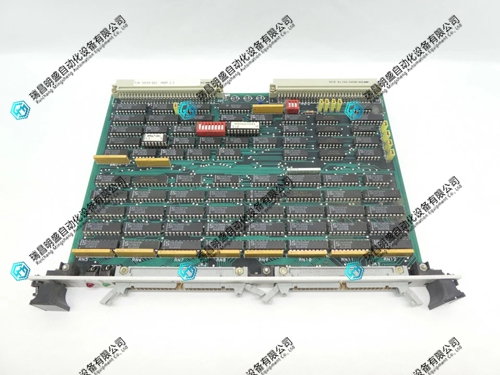

Xycom XVME-240数字输入/输出模块 PDF资料

1.产 品 资 料 介 绍:

XYCOM XVME-240 数字输入/输出模块 是一款基于 VMEbus 架构的高密度数字I/O模块,主要用于工业自动化系统中的开关量采集与控制输出,适合对并行数据处理要求较高的应用场景。

一、产品概述

型号:XVME-240

类型:数字输入/输出模块(DIO)

总线结构:VMEbus

信号类型:TTL电平

通道数量:64路

该模块集输入与输出功能于一体,可灵活配置各通道方向,用于实现设备间的高速数据交互。

二、核心功能特点

提供64路数字I/O通道,按字节分组管理

每组端口支持独立设置为输入或输出

支持多路中断输入功能,提升系统响应能力

配备标志输出信号,用于状态指示或握手控制

支持中断屏蔽与触发方式配置

适用于高速数字信号处理场合

三、工作原理

模块通过VME总线与主控制器通信,各I/O端口通过寄存器进行配置:

输入模式:采集外部设备状态信号

输出模式:向外部设备发送控制信号

中断输入:当信号变化时触发中断请求

该方式实现了数据的实时交互与快速响应。

四、技术特点

TTL逻辑电平接口,适配数字电路系统

支持边沿触发中断(上升沿/下降沿)

支持多种地址空间映射方式

具备较高的数据传输效率

The XYCOM XVME-240 digital input/output module is a high-density digital I/O module based on the VMEbus architecture, mainly used for switch quantity acquisition and control output in industrial automation systems, suitable for application scenarios with high requirements for parallel data processing.

1、 Product Overview

Model: XVME-240

Type: Digital Input/Output Module (DIO)

Bus structure: VMEbus

Signal type: TTL level

Number of channels: 64

This module integrates input and output functions, and can flexibly configure the direction of each channel to achieve high-speed data exchange between devices.

2、 Core functional features

Provide 64 digital I/O channels, managed by byte grouping

Each group of ports supports independent setting as input or output

Support multiple interrupt input functions to enhance system responsiveness

Equipped with flag output signals for status indication or handshake control

Support interrupt blocking and trigger configuration

Suitable for high-speed digital signal processing applications

3、 Working principle

The module communicates with the main controller through the VME bus, and each I/O port is configured through registers:

Input mode: Collect external device status signals

Output mode: Send control signals to external devices

Interrupt input: Trigger interrupt request when signal changes

This method achieves real-time interaction and rapid response of data.

4、 Technical features

TTL logic level interface, compatible with digital circuit systems

Support edge triggered interrupts (rising edge/falling edge)

Support multiple address space mapping methods

Has high data transmission efficiency