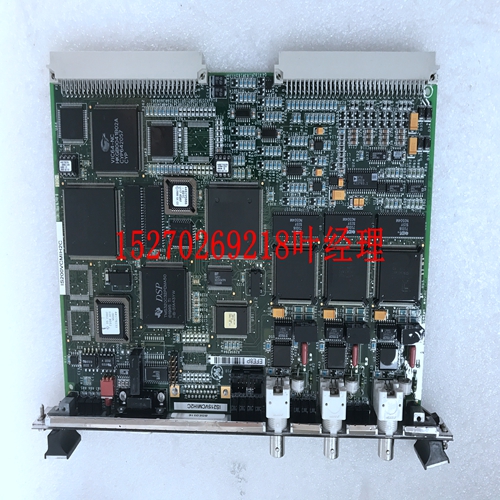

IS200IGPAG2A模块控制器

有限公司或其附属公司。保留所有权利。8-73 ID102715非机密8.4独占传输限制以下限制适用于独占传输:•必须进行一次数据传输。•必须指示为突发型SINGLE或突发型INCR。•不得包含BUSY转账。•地址必须与HSIZE指示的数据大小对齐。•HPROT信号的值必须确保独占访问监视器能够看到传输。注:HPROT信号必须确保专用访问监视器能够看到传输。如果独占访问监视器位于系统缓存的下游,则传输必须是不可缓存的。如果独占访问监视器位于系统缓存的上游,则允许传输可缓存。要将独占读取传输和独占写入传输视为同一独占访问序列的一部分,两种传输的以下信号必须相同:•HADDR,地址。•HSIZE,数据大小。•HPROT,保护控制。•HBURST,突发型。•HMASTER,主标识符。•HNONSEC,非安全,如适用。允许主机发出“独占读取”传输,并且在同一“独占”访问序列中,决不能在其后进行“独占写入”传输。允许主机发出“独占写入”传输,该传输之前未在同一“独占”访问序列中进行“独占读取”传输。在这种情况下,独占写入传输必须失败,并且必须解除HEXOKAY响应信号。一个主机在同一时间点不能有两个未完成的独占传输。当早期独占传输的数据阶段正在进行时,不得发出独占传输的地址阶段。无论传输是否属于同一独占访问序列,这都适用。当具有不同HMASTER值的早期独占传输的数据阶段正在进行时,允许发出具有特定HMASTER的独占传输的地址阶段。注:独占传输的地址阶段定义为HEXCL被断言且HTRANS指示NONSEQ时。当HTRANS指示IDLE时,HEXCL的断言未定义为独占传输的地址阶段。8独家转让8.4独家转让限制8-74 ARM Limited或其附属公司版权。保留所有权利。ARM IHI 0033B.b非机密ID102715 ARM IHI 0023B.b版权所有ARM Limited或其附属公司。保留所有权利。9-75 ID102715非机密第9章原子性本章定义了两种原子性质。它包含以下部分:•第9-76页上的单副本原子大小。•第9-77页的多拷贝原子性。9原子性9.1单拷贝原子性大小9-76版权所有ARM Limited或其附属公司。保留所有权利。ARM IHI 0033B.b非机密ID102715 9.1单副本原子大小单副本原子性大小定义保证传输以原子方式更新的数据字节数。为正在通信的一组组件定义单副本原子大小。例如:•处理器、DSP和DRAM控制器属于64位单拷贝原子组。•更大的组,包括处理器、DSP、DMA、DRAM、SRAM和外围设备,属于32位单拷贝原子组。传输的单个副本原子性保证永远不会超过其起始地址的对齐。例如,未与8字节边界对齐的64位单副本原子组中的突发没有任何64位单拷贝原子性保证。当写入传输更新内存位置时,必须保证观察者能够看到:•不更新该位置。•至少对单个副本原子大小的数据量进行更新。不允许另一个观察者在一个时间点看到在单拷贝原子大小内更新的一些数据字节,然后在稍后的时间点看到相同单拷贝原子尺寸内的其他数据字节。与传输相关的字节选通不会影响单个副本原子大小。要求大于单拷贝原子大小的传输必须以至少具有单拷贝原子性大小的块更新内存。注意:在确定单个副本原子性大小时,不考虑数据值更新的确切时刻。必须确保的是,任何主机都不能观察到原子数据的部分更新形式。例如,在许多系统中,数据结构

Limited or its affiliates. All rights reserved. 8-73 ID102715 Non-Confidential 8.4 Exclusive Transfer restrictions The following restrictions apply to an Exclusive Transfer: • Must have a single data transfer. • Must be indicated as burst type SINGLE or burst type INCR. • Must not include a BUSY transfer. • The address must be aligned to data size as indicated by HSIZE. • The value of the HPROT signals must guarantee that the Exclusive Access Monitor has visibility of the transfer. Note The HPROT signals must guarantee that the Exclusive Access Monitor has visibility of the transfer. If the Exclusive Access Monitor is located downstream of a system cache, then the transfer must be Non-cacheable. If the Exclusive Access Monitor is located upstream of a system cache, then it is permitted for the transfer to be Cacheable. For an Exclusive Read transfer and an Exclusive Write transfer to be considered part of the same Exclusive access sequence, the following signals must be the same for both transfers: • HADDR, Address. • HSIZE, Data Size. • HPROT, Protection Control. • HBURST, Burst Type. • HMASTER, Master Identifier. • HNONSEC, Non-secure, if applicable. It is permitted for a master to issue an Exclusive Read transfer and never follow it with an Exclusive Write transfer in the same Exclusive access sequence. It is permitted for a master to issue an Exclusive Write transfer, which has not been preceded by an Exclusive Read transfer in the same Exclusive access sequence. In this case, the Exclusive Write transfer must fail and the HEXOKAY response signal must be deasserted. A master must not have two Exclusive Transfers outstanding at the same point in time. The address phase of an Exclusive Transfer must not be issued while the data phase of an earlier Exclusive Transfer is in progress. This applies whether the transfers are part of the same Exclusive access sequence or not. It is permitted for the address phase of an Exclusive Transfer with a particular HMASTER value to be issued while the data phase of an earlier Exclusive Transfer with a different HMASTER value is in progress. Note The address phase of an Exclusive Transfer is defined as being when HEXCL is asserted and HTRANS indicates NONSEQ. The assertion of HEXCL when HTRANS indicates IDLE is not defined as the address phase of an Exclusive Transfer. 8 Exclusive Transfers 8.4 Exclusive Transfer restrictions 8-74 Copyright ARM Limited or its affiliates. All rights reserved. ARM IHI 0033B.b Non-Confidential ID102715 ARM IHI 0033B.b Copyright ARM Limited or its affiliates. All rights reserved. 9-75 ID102715 Non-Confidential Chapter 9 Atomicity This chapter defines two atomic properties. It contains the following sections: • Single-copy atomicity size on page 9-76. • Multi-copy atomicity on page 9-77. 9 Atomicity 9.1 Single-copy atomicity size 9-76 Copyright ARM Limited or its affiliates. All rights reserved. ARM IHI 0033B.b Non-Confidential ID102715 9.1 Single-copy atomicity size The single-copy atomicity size defines the number of data bytes that a transfer is guaranteed to update atomically. The single-copy atomicity size is defined for a group of components that are communicating. For example: • A processor, DSP, and DRAM controller are in a 64-bit single-copy atomic group. • A larger group, including a processor, DSP, DMA, DRAM, SRAM, and peripherals are in a 32-bit single-copy atomic group. A transfer never has a single-copy atomicity guarantee greater than the alignment of its start address. For example, a burst in a 64-bit single-copy atomic group that is not aligned to an 8-byte boundary does not have any 64-bit single-copy atomicity guarantee. When a write transfer updates a memory location, it must be guaranteed that an observer will see either: • No update to the location. • An update to at least a single-copy atomicity size amount of data. It is not permitted for another observer to see some data bytes updated within the single-copy atomicity size at one point in time, and then other data bytes within the same single-copy atomicity size at a later point in time. Byte strobes associated with a transfer do not affect the single-copy atomicity size. It is required that a transfer that is larger than the single-copy atomicity size must update memory in blocks of at least the single-copy atomicity size. Note When determining the single-copy atomicity size the exact instant when the data value is updated is not considered.What must be ensured is that no master can ever observe a partially updated form of the atomic data. For example, in many systems data structures