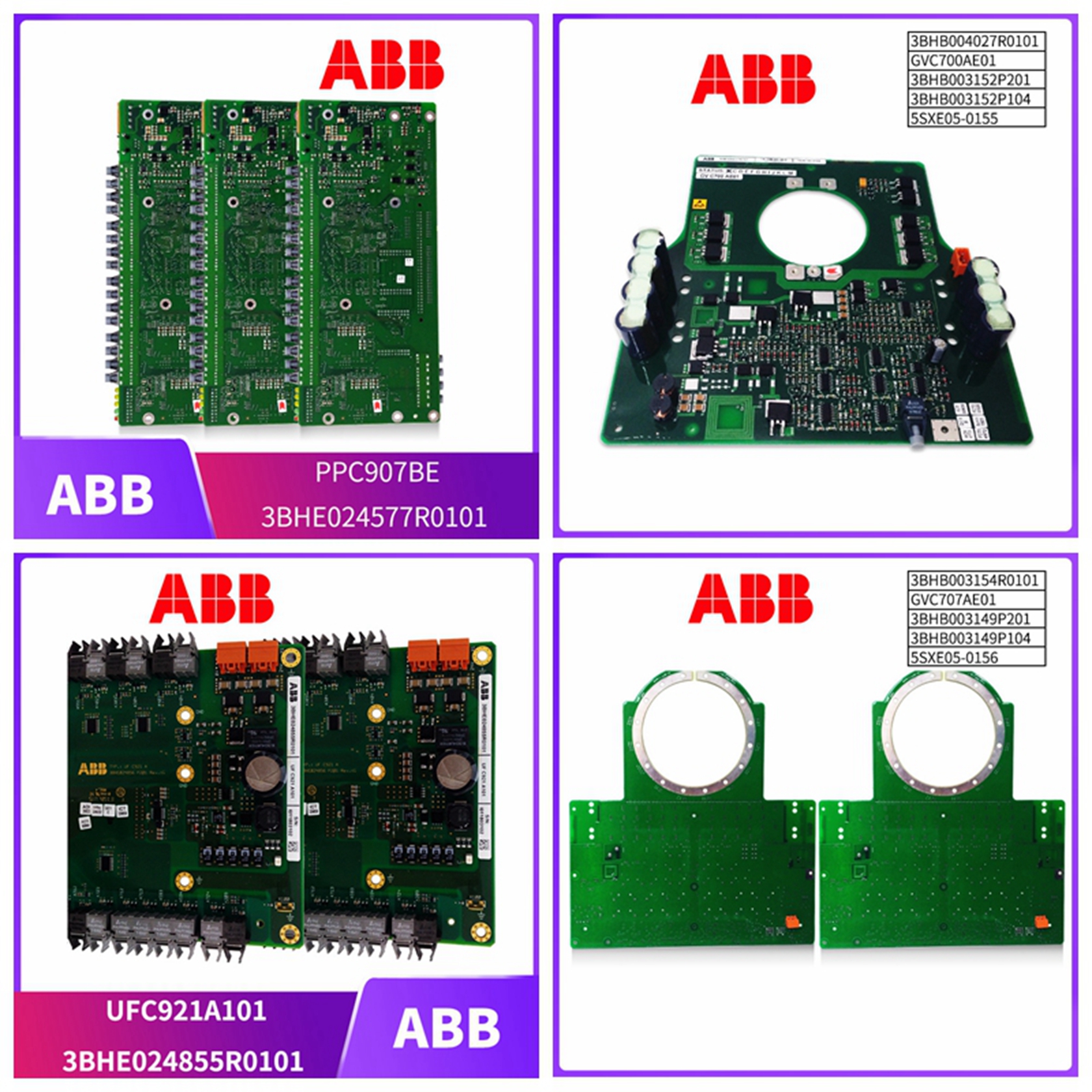

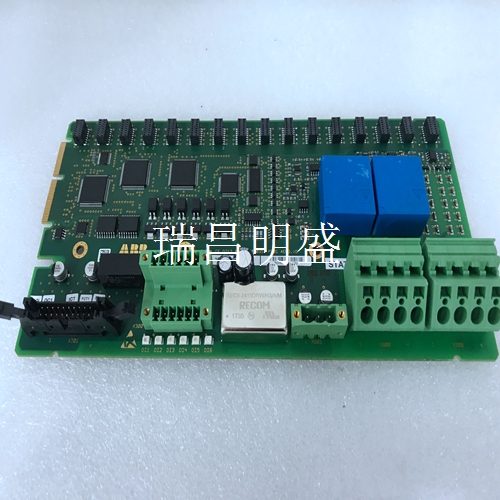

5751017-L DSTC456工控备件PLC模块DCS系统模块

PCI中断启用(位8)用作全局PCI中断启用

在任何一级或二级中断源将导致PCI中断之前,除其他使能位外,它必须设置为高(1)。INTCSR位0、6和7与存储器奇偶校验电路有关。不幸的是,PLX9656没有提供一种直接的、第一层的方式来断言来自奇偶校验错误的PCI中断。相反,将位0和位6都设置为高仅允许奇偶校验错误断言称为LSERR#的外部引脚。LSERR#信号被路由到称为LISR的第二层中断控制寄存器。LISR是RFM控制和状态寄存器。通过LISR,奇偶校验故障必须断言另一个称为LINTi#的外部信号,该信号在第15位通过INTCSR返回,最后到达PCI中断。有关奇偶校验错误中断路径的可视表示, 中断电路框图图1。 操作相关的INTCSR中断启用。

PCI interrupt enable (bit 8) used as global PCI interrupt enable

Before any level 1 or level 2 interrupt source will cause PCI interrupt, it must be set to high (1) in addition to other enable bits. The INTCSR bits 0, 6, and 7 are related to the memory parity circuit. Unfortunately, the PLX9656 does not provide a direct, layer 1 way to assert PCI interrupts from parity errors. Instead, setting both bits 0 and 6 high allows only parity error assertions on external pins called LSERR #. The LSERR # signal is routed to the Layer 2 interrupt control register called LISR. LISR is an RFM control and status register. Through LISR, parity failure must assert another external signal called LINTi #, which returns through INTCSR at bit 15 and finally reaches PCI interrupt. For the visual representation of the parity error interrupt path, the interrupt circuit block diagram is shown in Figure 1. The operation related INTCSR interrupt is enabled.

配置寄存器

在的正常操作期间,CNTRL寄存器的使用有限。CNTRL中的大多数位将保持其PCI重置默认值。一个例外是位28(编程串行EEPROM存在),一旦串行EEPROM初始化完成,该位应从默认值0变为1。CNTRL寄存器的位30用作部分软件复位。当PCI写入将位30设置为高(1)时,PLX设备内的运行时寄存器和DMA寄存器不受影响。然而,PLX本地配置寄存器和中PLX设备以外的所有部分保持复位,直到位30设置为低(0)。这包括所有RFM控制和状态寄存器及其相关电路、发射FIFO和发射器电路、接收器FIFO与接收器电路。在软件复位期间,禁止PCI总线访问RFM控制和状态寄存器以及访问反射存储器。此外,由于反射存储器的刷新被禁止,因此先前存储在反射存储器中的所有数据都可能损坏。最后,当处于重置状态时,传递到重置节点和所有下游节点的网络数据将丢失。下游节点是那些连接到重置节点的发射机的节点。一旦CNTRL寄存器的位30被设置为低(0),用户必须将CNTRL计数器的位29设置为高(1),然后设置为低电平(0)以重新初始化PLX本地配置寄存器。

Configuration register

During normal operation of, the use of the CNTRL register is limited. Most bits in CNTRL will maintain their PCI reset defaults. One exception is bit 28 (programmed serial EEPROM present), which should change from the default value of 0 to 1 once serial EEPROM initialization is complete. Bit 30 of the CNTRL register is used as a partial software reset. When PCI Write sets bit 30 high (1), the runtime registers and DMA registers in the PLX device are not affected. However, all parts of the PLX local configuration register and except for the PLX device in remain reset until bit 30 is set to low (0). This includes all RFM control and status registers and their associated circuits, transmit FIFO and transmitter circuits, receiver FIFO and receiver circuits. During a software reset, the PCI bus is prohibited from accessing the RFM control and status registers and from accessing reflective memory. In addition, since the refresh of the reflection memory is prohibited, all data previously stored in the reflection memory may be damaged. Finally, when in the reset state, the network data transferred to the reset node and all downstream nodes will be lost. Downstream nodes are those nodes connected to the transmitter of the reset node. Once bit 30 of the CNTRL register is set to low (0), the user must set bit 29 of the CNTRL counter to high (1) and then to low (0) to reinitialize the PLX local configuration register.