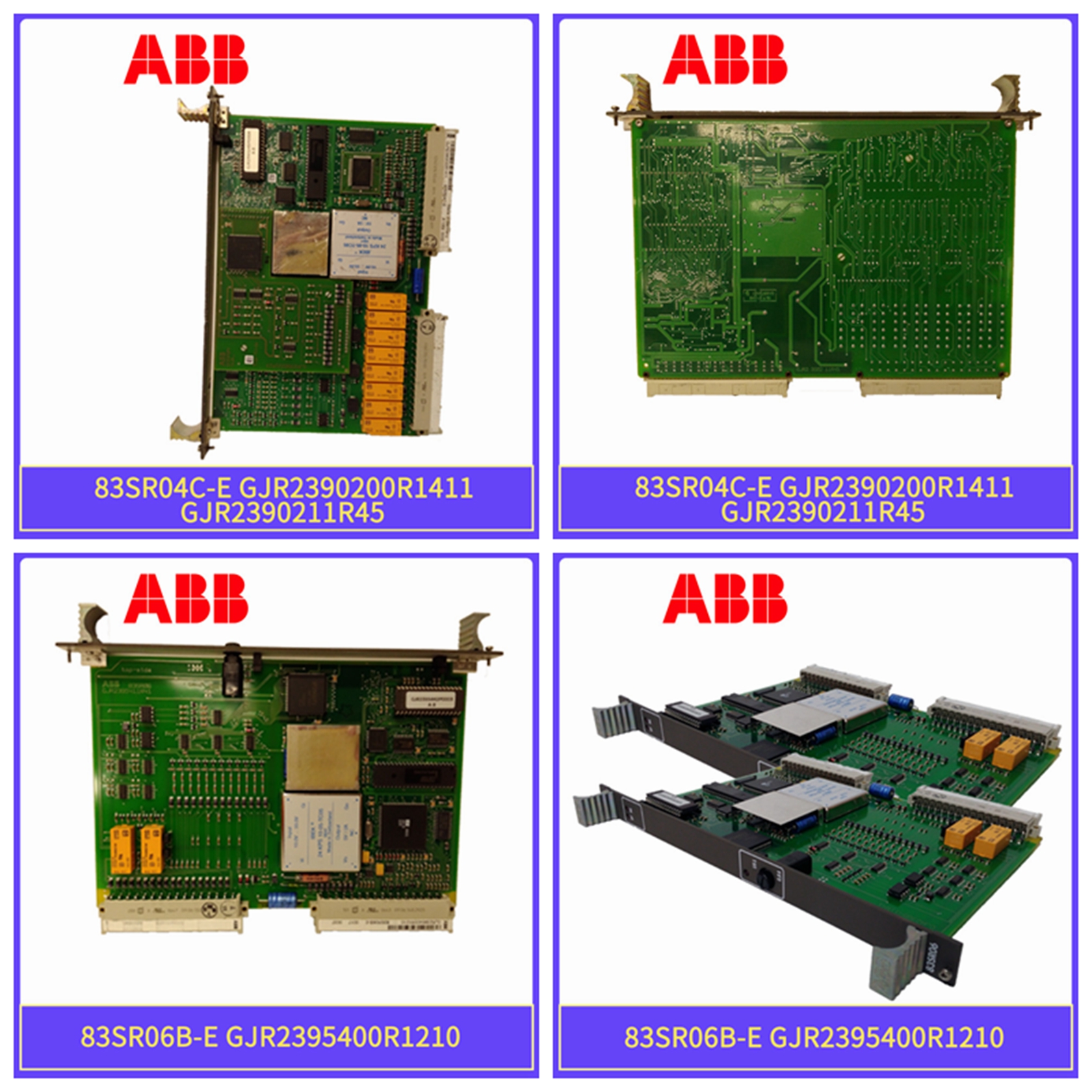

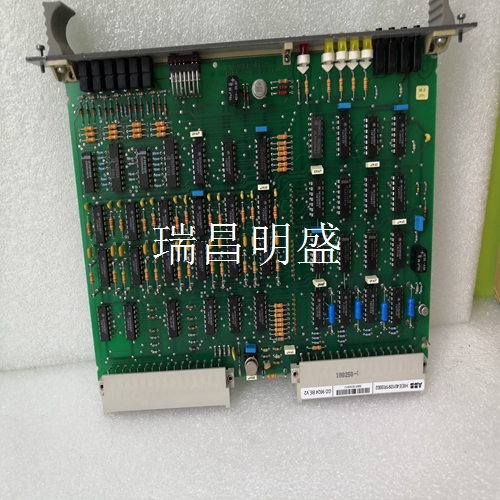

5750001-ER PLC控制器

网络中断

除了数据外,还能够通过网络传递中断数据包。网络中断分组可以被定向到特定节点或全局广播到网络上的所有节点。每个网络中断包包含发送方的节点ID、目标(目的地)节点ID、中断类型信息和32位用户定义的数据。网络中断的类型包括三(3)个通用中断、一个网络初始化中断和一个复位节点请求中断。发送节点使用三个RFM控制和状态寄存器指定目标(目的地)节点、中断类型和32位数据。每个接收节点在中断分组通过时评估它们。如果中断指向该节点,则发送方的节点ID存储在相应的发送方ID FIFO(四个之一)中。发件人ID FIFO有127个位置深。数据将存储在伴随的127个位置的深度数据FIFO中。如果通过LISR、LIER和INTCSR寄存器启用,四个可能的网络中断中的任何一个也可以在每个接收节点生成主机PCI中断。网络初始化中断很像三个通用中断之一,如果需要,可以用作第四个通用中断。但是,它确实有一个附加功能。当由于加电或复位而初始化时,本地处理器可以向网络上的所有其他节点全局生成网络初始化中断。此事件可用于通知主机系统或另一个(主)节点,该节点上的某部分内存需要重新初始化。重置节点请求中断不像其他四个网络中断那样存储在FIFO中。此外,它不会导致电路板立即复位。相反,它只能在LISR寄存器中设置一位,如果启用,将导致PCI中断。实际的板复位应由主机系统以有序的方式执行。

Network interruption

In addition to data, interrupt packets can also be transmitted over the network. Network interrupt packets can be directed to specific nodes or broadcast globally to all nodes on the network. Each network interrupt packet contains the sender's node ID, destination node ID, interrupt type information, and 32-bit user-defined data. The types of network interrupts include three (3) general interrupts, one network initialization interrupt, and one reset node request interrupt. The sending node uses three RFM control and status registers to specify the destination node, interrupt type, and 32-bit data. Each receiving node evaluates interrupt packets as they pass. If the interrupt points to this node, the sender's node ID is stored in the corresponding sender ID FIFO (one of four). The sender ID FIFO has 127 positions deep. The data will be stored in the accompanying 127 position depth data FIFO. If enabled through LISR, LIER and INTCSR registers, any of the four possible network interrupts can also generate a host PCI interrupt at each receiving node. The network initialization interrupt is very similar to one of the three general interrupts. If necessary, it can be used as the fourth general interrupt. However, it does have an additional function. When initializing due to power on or reset, the local processor can generate a network initialization interrupt globally to all other nodes on the network. This event can be used to notify the host system or another (master) node that some memory on that node needs to be reinitialized. The reset node request interrupt is not stored in the FIFO like the other four network interrupts. In addition, it does not cause the board to reset immediately. On the contrary, it can only set one bit in the LISR register. If it is enabled, it will cause PCI interrupt. The actual board reset should be performed by the host system in an orderly manner.