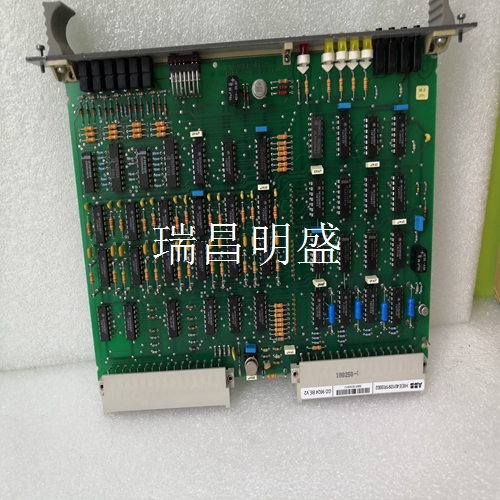

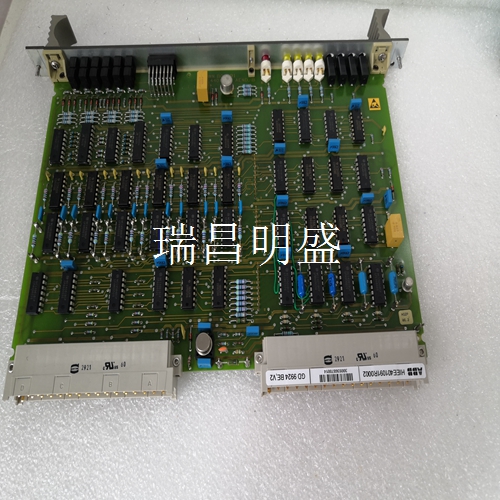

57310001-KT/1 DSTC176工控系统系列产品卡件模块

反射内存

RAM实际的板载反射内存SDRAM有两种大小:64MB或128 MB,具有奇偶校验。SDRAM从基本地址寄存器3中指定的位置开始(PLX将该地址空间称为“本地地址空间1”)。与之前版本的GE反射式存储器产品不同,RFM控制和状态寄存器不会取代前40美元的RAM位置。对于64MB选项,偏移地址范围为$0至$3FFFFFF,对于128MB选项,则为$0到$7FFFF。奇偶校验功能上电时不启用奇偶校验函数,必须通过将本地配置寄存器INTCSR中的位0、6和7设置为偏移量$68,以及将RFM控制和状态寄存器的本地中断启用(LIER)寄存器中的位13设置为偏移值$14来启用。要使用奇偶校验,写入必须发生在32位(L字)或64位(Q字)边界上。奇偶校验有效时,禁止8位(字节)写入和16位(字)写入。此外,由于RAM在有效的奇偶校验状态下没有加电,因此要用奇偶校验读取的任何位置必须首先通过写入某些数据模式来初始化。否则,读取将断言错误的奇偶校验错误。

Reflective memory

RAM The actual onboard reflective memory SDRAM has two sizes: 64MB or 128 MB, with parity. SDRAM starts at the location specified in the basic address register 3 (PLX refers to this address space as "local address space 1"). Unlike previous versions of GE reflective memory products, RFM control and status registers do not replace the first $40 of RAM locations. The offset address range is $0 to $3FFFFFF for the 64MB option and $0 to $7FFFF for the 128MB option. The parity function is not enabled when the parity function is powered on. It must be enabled by setting bits 0, 6, and 7 in the local configuration register INTCSR to offset $68 and bit 13 in the local interrupt enable (LIER) register of the RFM control and status registers to offset $14. To use parity, writes must occur on a 32-bit (L word) or 64 bit (Q word) boundary. When parity is valid, 8-bit (byte) writing and 16 bit (word) writing are prohibited. In addition, since RAM is not powered up in the valid parity state, any location to be read with parity must first be initialized by writing some data patterns. Otherwise, reading asserts an incorrect parity error.

寄存器

中断电路有一个PCI中断输出(INTA#)。上的一个或多个事件可能导致中断。PCI中断的源可以通过几个寄存器单独启用和监控。的中断电路分为两层。本地配置寄存器的INTCSR在PLX设备中启用并监控第一层中断,偏移量为$68。监控第一层的可选源包括:1.本地到PCI门铃寄存器2.消息传出后队列不为空3.主/目标中断状态4.作为PCI总线主控器的256次连续PCI重试5。DMA通道0完成/终端计数6.DMA通道1完成/终端数7.本地中断输入(LINTi#)上面列出的第一层源(1)和(2)在中的使用有限。第一层源的使用由主机系统要求决定。第一层源(5)和(6)在DMA周期期间使用,并且必须在DMA寄存器中进一步配置。最后一级中断源(7)是本地中断输入(LINTi#)。LINTi#信号是PLX设备的实际物理输入,由于所有二级中断都通过LINTi#传输,因此具有重要意义。第二层中断包括几个操作故障和四个网络中断。通过两个RFM控制和状态寄存器(称为本地中断状态寄存器(LISR)和LIER)选择和监控第二层中断。有关两个寄存器的详细说明,请参阅编程部分。

register

The interrupt circuit has a PCI interrupt output (INTA #). One or more events on may cause an interruption. The source of PCI interrupts can be enabled and monitored separately through several registers. The interrupt circuit of is divided into two layers. The INTCSR of the local configuration register enables and monitors layer 1 interrupts in the PLX device with an offset of $68. The optional sources for monitoring the first layer include: 1. Local to PCI doorbell register 2. The queue is not empty after the message is sent out 3. Master/target interrupt status 4. 256 consecutive PCI retries as the PCI bus master 5. DMA channel 0 completion/terminal count 6. DMA channel 1 completion/number of terminals 7. The first layer sources (1) and (2) listed above the local interrupt input (LINTi #) have limited use in. The use of the first tier source is determined by the host system requirements. The first layer sources (5) and (6) are used during the DMA cycle and must be further configured in the DMA register. The last level interrupt source (7) is the local interrupt input (LINTi #). LINTi # signal is the actual physical input of the PLX device. Since all secondary interrupts are transmitted through LINTi #, it is of great significance. Layer 2 outages include several operational failures and four network outages. Layer 2 interrupts are selected and monitored through two RFM control and status registers, called the Local Interrupt Status Register (LISR) and the LIER. For a detailed description of the two registers, see the Programming section.