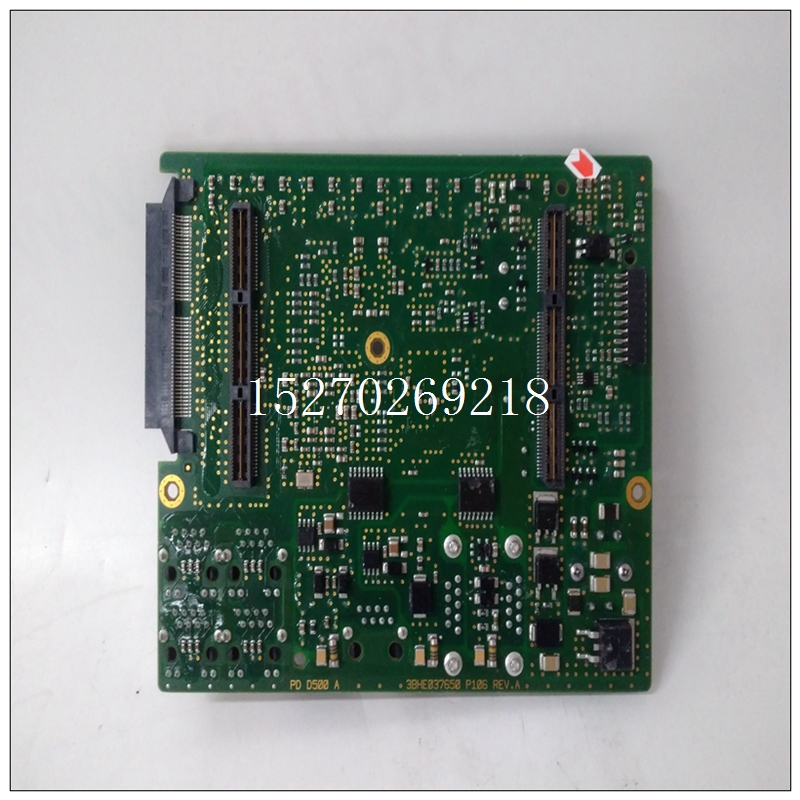

PDD500A101使用流程,ABB处理器

智能计数器/控制器支持两个VMEbus中断器模块,可断言两个模块中的任何一个同时IRQ水平。检修时,断路器模块以8位中断向量和自动清除挂起的IRQ。CPU保持内存中挂起的中断事件队列,写入新的当前一个事件发生时,中断器模块的IRQ变明朗。共模电压限制:±25 V差模电压限制:±5 V由于以下原因,差动电压范围限制为±5 V:a 1/4瓦,

PDD500A101使用流程120Ω 终端电阻器VIH/VIL差分模式:RS-422兼容差动输入VIH:在主(正)输入时发生电压比压差大100 mV共模内的(负)输入电压电压范围为±25 V。VIL:在主(正)输入时发生电压比压差小100 mV(负极)共模电压范围内的输入电压±25 V。VIH/VIL单极(单端)模式(差分输入连接到VTTL):VIH=VTTL+100 mVVIL=VTTL-100 mV输入滞后:50 mV输入上升时间建议:最小上升时间-5 ns传播延迟-25 ns典型值最大上升时间-1毫秒VMIVME-2540能够接受不同的输入在电压和时域上有很大的优势。必须注意在以下情况下,确保输入电压在VTTL周围稳定:在单端模式下,将产生虚假数据。同样,在使用差分输入时,必须小心为确保输入不允许随相互之间或数据之间的电压值在100 mV以内可以生成转换。

The Intelligent Counter/Controller supports two

VMEbus interrupter modules which may assert any of two

IRQ levels simultaneously. When serviced, the interrupter

modules respond with an 8-bit interrupt vector and

automatically clear the pending IRQ. The CPU maintains a

queue of pending interrupt events in memory, writing a new

IRQ to the interrupter modules when the previous event is

cleared.Common-Mode Voltage Limit: ±25 V

Differential Mode Voltage Limit: ±5 V

The differential voltage range is limited to ±5 V due to

a 1/4 W, 120 Ω termination resistor

VIH/VIL Differential Mode: RS-422-compliant

differential input

VIH: Occurs whenever the primary (positive) input

voltage is 100 mV greater than the differential

(negative) input voltage within the common-mode

voltage range of ±25 V.

VIL: Occurs whenever the primary (positive) input

voltage is 100 mV less than the differential (negative)

input voltage within the common-mode voltage range

of ±25 V.

VIH/VIL Unipolar (Single-Ended) Mode

(Differential Input Connected to VTTL):

VIH = VTTL + 100 mV

VIL = VTTL - 100 mV

Input Hysteresis: 50 mV

Input Rise Time Recommendations:

Minimum rise time - 5 ns

Propagation delay - 25 ns typical

Maximum rise time - 1 msThe AM26LS33A differential receivers used on the

VMIVME-2540 are capable of accepting inputs that vary

greatly on voltage and time domain. Care must be taken to

ensure that the input voltages are stable around VTTL when

in single-ended mode or spurious data will be produced.

Similarly, when using differential inputs, care must be taken

to ensure that the inputs, are not allowed to float with

voltage values within 100 mV of each other or data

transitions may be generated.