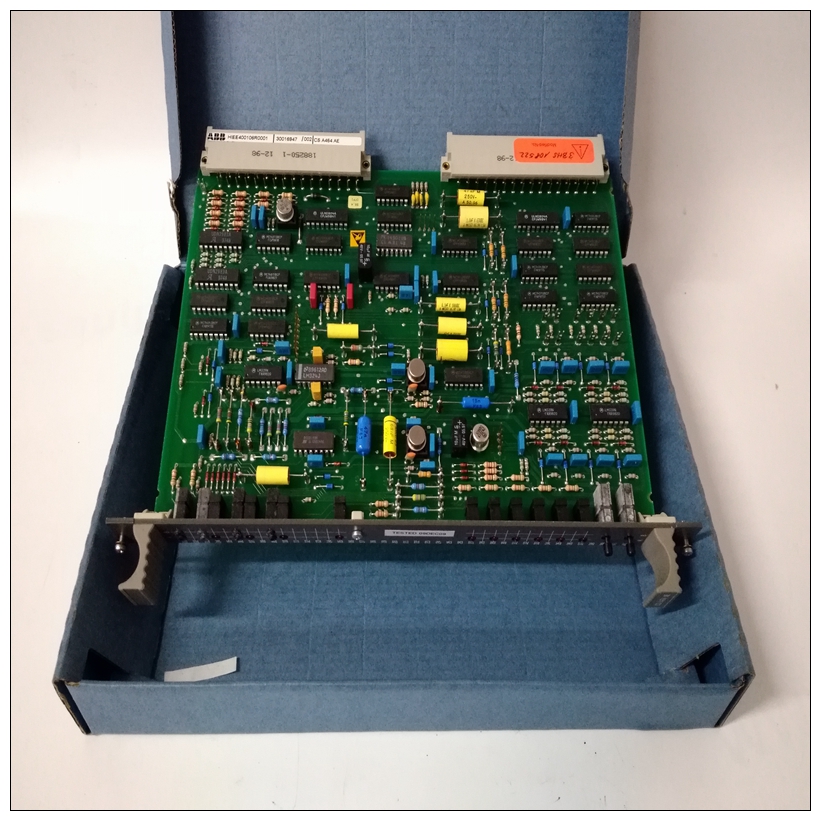

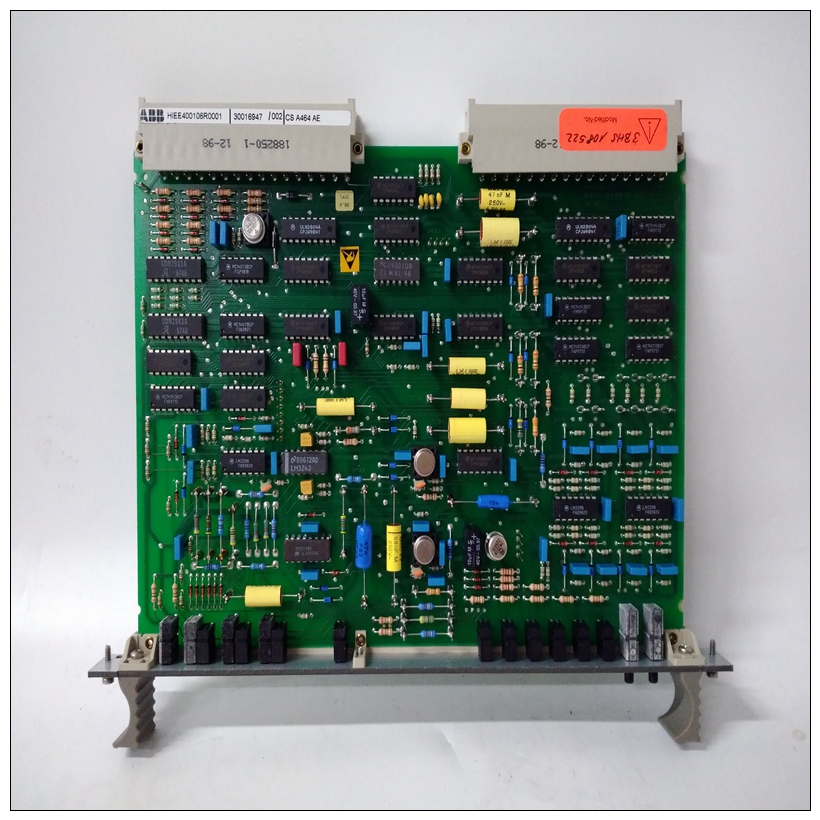

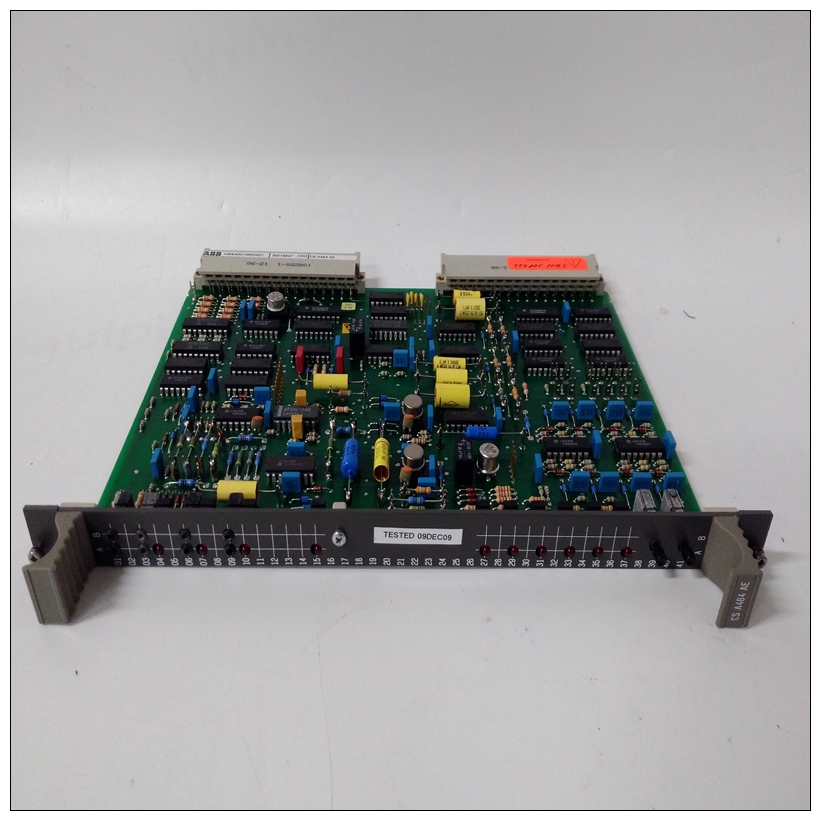

HIEE400106R0001模块,ABB产品尺寸

由PIB中的端口92寄存器控制的功能(当MVME2603/2604为系统时,重置VMEbus控制器)

5、由时钟除数寄存器控制的PCI/ISA输入/输出复位功能在PIB中6.VMEbus系统重置∗ 信号

7.Universe ASIC(PCI/VME总线)的VMEbus重置源桥架控制器):系统软件重置和本地软件重置。下表显示了受各种类型影响的设备重置次数。

HIEE400106R0001模块有关使用重置的详细信息,请参阅MVME2600系列单附录D中列出的Board Computer Programmer参考指南,相关文档Endian问题MVME2603/2604支持两种little endian(例如,Windows NT)和big-endian(例如AIX)软件。PowerPC处理器和VMEbus本身就是big-endian,而PCI总线是big-endian天生的小端。以下各节总结了MVME2603/2604处理大型和小型计算机中的软件和硬件差异小端运算。有关endian注意事项的更多详细信息,请参阅MVME2600系列单板计算机程序员参考指南,见附录D,相关文件。处理器/内存域MPC603/604处理器可以在大端和小端模式。然而,它总是处理外部通过执行地址将处理器/内存总线作为大端在小端模式下运行时重新排列和排序。这个Raven MPU/PCI总线网桥控制器ASIC和Falcon内存控制器芯片组,以及DRAM、ROM/Flash和系统寄存器,始终显示为大端。Raven ASIC的作用由于PCI总线是little endian,Raven在中执行字节交换从PCI到内存和从处理器到PCI的两个方向在编程以大端运算时保持地址不变处理器和内存子系统的模式。在little endian模式下,Raven反向重新排列PCIbound访问的地址,并重新排列内存绑定访问的地址(来自PCI)。在这种情况下,不进行字节交换。PCI域PCI总线本质上是小端的。所有直接连接到的设备PCI总线在little endian模式下运行,而与处理器域中的操作。

ALT_RST∗ function controlled by the Port 92 register in the PIB

(resets the VMEbus when the MVME2603/2604 is system

controller)

5. PCI/ISA I/O Reset function controlled by the Clock Divisor register

in the PIB

6. The VMEbus SYSRESET∗ signal

7. VMEbus Reset sources from the Universe ASIC (PCI/VME bus

bridge controller): the System Software reset and Local Software

Reset.

The following table shows which devices are affected by the various types

of resets. For details on using resets, refer to the MVME2600 Series Single

Board Computer Programmer’s Reference Guide, listed in Appendix D,

Related DocumentationEndian Issues

The MVME2603/2604 supports both little-endian (for example,

Windows NT) and big-endian (for example, AIX) software. The PowerPC

processor and the VMEbus are inherently big-endian, while the PCI bus is

inherently little-endian. The following sections summarize how the

MVME2603/2604 handles software and hardware differences in big- and

little-endian operations. For further details on endian considerations, refer

to the MVME2600 Series Single Board Computer Programmer’s

Reference Guide, listed in Appendix D, Related Documentation.

Processor/Memory Domain

The MPC603/604 processor can operate in both big-endian and

little-endian mode. However, it always treats the external

processor/memory bus as big-endian by performing address

rearrangement and reordering when running in little-endian mode. The

MPC registers in the Raven MPU/PCI bus bridge controller ASIC and the

Falcon memory controller chip set, as well as DRAM, ROM/Flash, and

system registers, always appear as big-endian.

Role of the Raven ASIC

Because the PCI bus is little-endian, the Raven performs byte swapping in

both directions (from PCI to memory and from the processor to PCI) to

maintain address invariance while programmed to operate in big-endian

mode with the processor and the memory subsystem.

In little-endian mode, the Raven reverse-rearranges the address for PCIbound accesses and rearranges the address for memory-bound accesses

(from PCI). In this case, no byte swapping is done.

PCI Domain

The PCI bus is inherently little-endian. All devices connected directly to

the PCI bus operate in little-endian mode, regardless of the mode of

operation in the processor’s domain.