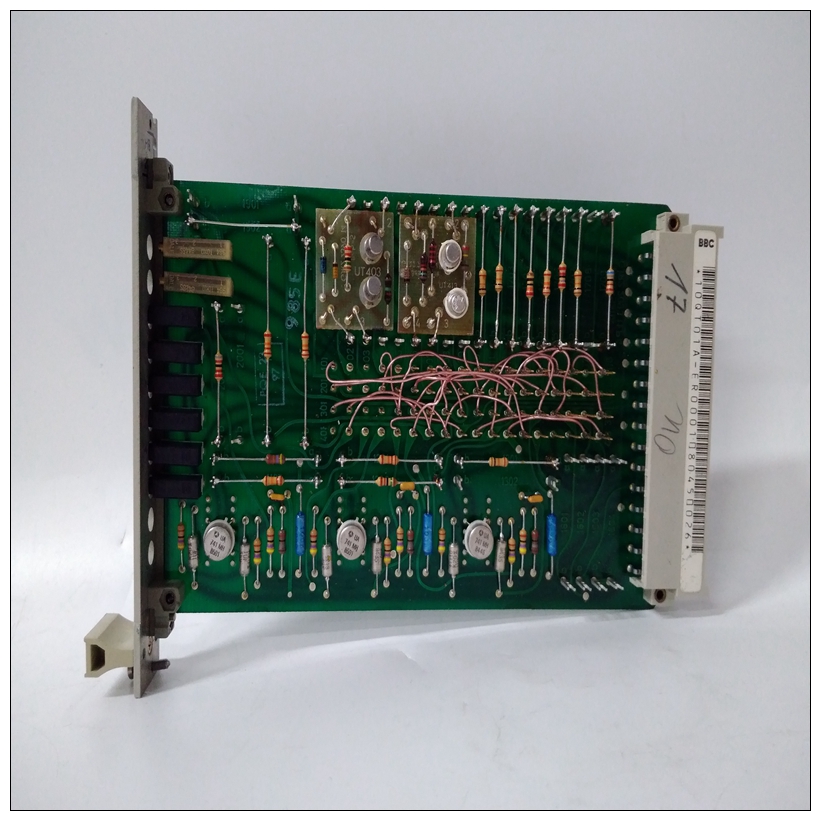

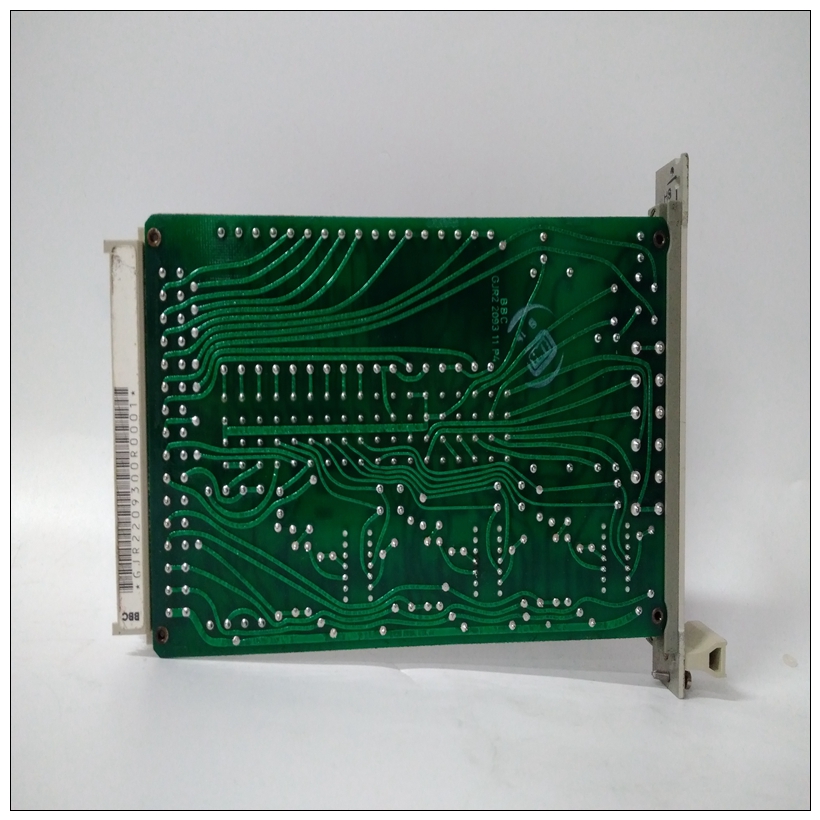

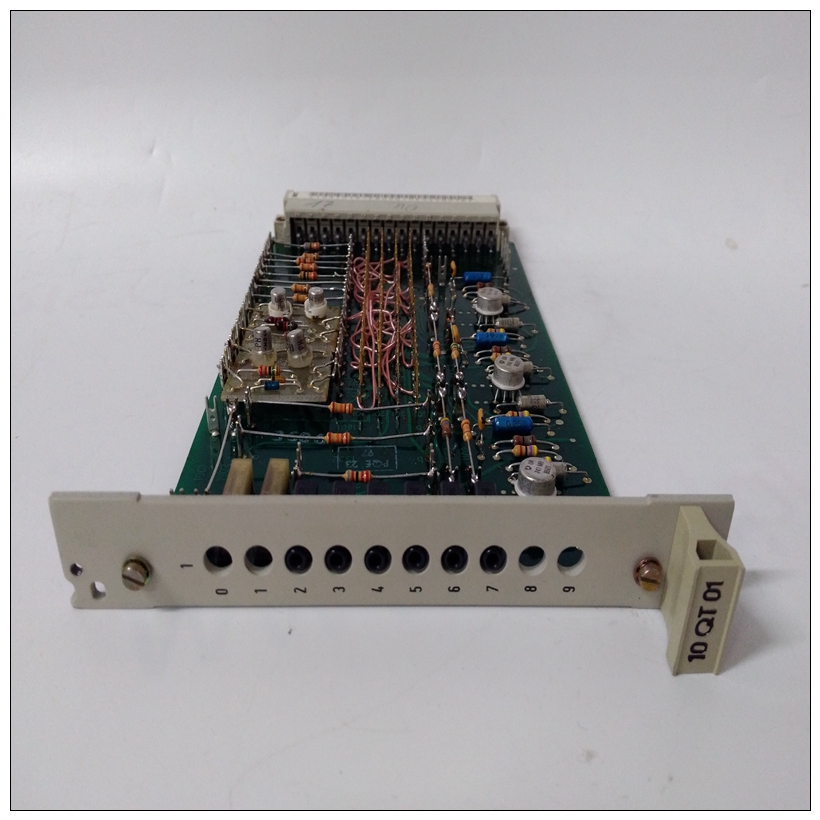

10QT01模块,ABB使用配置说明

总线开关ASIC提供处理器总线之间的接口(MC88110总线)和本地外围总线(MC68040兼容总线)。参考MVME197LE框图(图1-1)。它提供总线仲裁MC88110总线,用作七级中断处理程序。它有两条总线的可编程地图解码器,以及上的写后缓冲区每个都有两个滴答计时器和四个32位通用寄存器。DCAM(DRAM控制器和地址多路复用器)ASIC提供DRAM的地址多路复用器和RAS/CA/写控制以及ECDM的数据控制。

10QT01模块ECDM(纠错和数据多路复用器)ASIC多路复用在DRAM阵列上的四条数据路径之间。由于设备处理16位,MVME197LE上需要四个这样的设备来容纳64位MC88110微处理器的数据总线。单位错误校正和在ECDM中执行双位检测。PCCchip2(外围通道控制器)ASIC提供两个滴答定时器以及与LAN芯片、SCSI芯片、串口芯片和打印机端口和BBRAM(电池备用RAM)。具有MC68040总线接口的VMEbus接口芯片是一种称为VMEchip2。VMEchip2包括两个滴答计时器、一个看门狗计时器、,用于主接口和从接口的可编程地图解码器,以及VMEbus到/来自本地外围总线DMA控制器,VMEbus到/来自本地外围总线非DMA编程访问接口,VMEbus中断器、VMEbus系统控制器、VMEbus中断处理程序和VMEbus请求者。本地外围总线到VMEbus的传输可以是D8、D16或D32。VMEchip2然而,到VMEbus的DMA传输可以与块传输一样宽64位(BLT)。要求这些电路板的设计应符合以下要求文件:❏ VMEbus规范(IEEE 1014-87)❏ EIA-232-D串行接口规范❏ SCSI规范,ANSI

The BusSwitch ASIC provides an interface between the processor bus

(MC88110 bus) and the local peripheral bus (MC68040 compatible bus). Refer

to the MVME197LE block diagram (Figure 1-1). It provides bus arbitration for

the MC88110 bus and serves as a seven level interrupt handler. It has

programmable map decoders for both busses, as well as write post buffers on

each, two tick timers, and four 32-bit general purpose registers.

The DCAM (DRAM Controller and Address Multiplexer) ASIC provides the

address multiplexers and RAS/CAS/WRITE control for the DRAM as well as

data control for the ECDM.

The ECDM (Error Correction and Data Multiplexer) ASIC multiplexes

between four data paths on the DRAM array. Since the device handles 16 bits,

four such devices are required on the MVME197LE to accommodate the 64-bit

data bus of the MC88110 microprocessor. Single-bit error correction and

double-bit detection is performed in the ECDM.

The PCCchip2 (Peripheral Channel Controller) ASIC provides two tick timers

and the interface to the LAN chip, the SCSI chip, the serial port chip, the

printer port, and the BBRAM (Battery Backup RAM).

A VMEbus interface chip with an MC68040 bus interface is one ASIC called the

VMEchip2. The VMEchip2 includes two tick timers, a watchdog timer,

programmable map decoders for the master and slave interfaces, and a

VMEbus to/from the local peripheral bus DMA controller, a VMEbus to/from

the local peripheral bus non-DMA programmed access interface, a VMEbus

interrupter, a VMEbus system controller, a VMEbus interrupt handler, and a

VMEbus requester.

Local peripheral bus to VMEbus transfers can be D8, D16, or D32. VMEchip2

DMA transfers to the VMEbus, however, can be 64 bits wide as Block Transfer

(BLT).

Requirements

These boards are designed to conform to the requirements of the following

documents:

❏ VMEbus Specification (IEEE 1014-87)

❏ EIA-232-D Serial Interface Specification, EIA

❏ SCSI Specification, ANSI